교재집필

RTL (Register-Transfer Level) 설계

서호60

2024. 12. 1. 14:19

**RTL(Register-Transfer Level)**은 디지털 회로 설계에서 하드웨어의 동작을 레지스터 간의 데이터 이동과 **조작(연산)**으로 설명하는 추상적인 설계 수준을 말합니다. RTL은 하드웨어 설명 언어(HDL, 예: Verilog, VHDL)를 사용하여 회로의 동작을 기술하는 방식이며, 디지털 설계의 중요한 단계 중 하나입니다.

RTL 설계의 주요 특징

- 레지스터 중심 설계

- 설계는 **레지스터(Register)**를 기준으로 데이터가 이동(Transfer)하고, 연산(Operation)이 수행되는 흐름으로 표현됩니다.

- 레지스터는 클럭 신호에 의해 값을 저장하고, 값은 다른 레지스터나 회로로 전달됩니다.

- 동작의 추상화 수준

- RTL은 게이트 수준보다 높은 추상화 수준으로 설계되며, 하드웨어의 논리적 동작에 중점을 둡니다.

- 설계자는 특정 동작(예: 덧셈, 조건 분기)을 정의하지만, 회로의 실제 물리적 배치는 자동화된 도구가 생성합니다.

- 동기식 설계

- RTL은 일반적으로 클럭 신호를 기반으로 데이터 이동과 동작이 동기화됩니다.

- 레지스터와 조합 논리(Combinational Logic)가 주요 구성 요소입니다.

RTL 설계의 표현 방식

- 레지스터와 데이터 이동

- 레지스터에 저장된 데이터가 조합 논리를 통해 처리된 후 다른 레지스터로 전송됩니다.

- 예: Reg_B <= Reg_A + 1

→ 레지스터 A의 값에 1을 더한 결과를 레지스터 B에 저장.

- 클럭 기반 동작

- 동작은 클럭 신호(예: posedge clk)에 따라 실행됩니다.

- 조건부 동작

- 특정 조건에서 데이터 이동 또는 연산이 수행됩니다.

- 예: if (enable) Reg_B <= Reg_A;

RTL과 다른 설계 수준의 비교

설계 수준설명사용 사례

| 행위 수준 | 기능만 기술하며, 하드웨어 구현 세부 사항은 다루지 않음. | 고수준 모델링 및 시뮬레이션 |

| RTL 수준 | 레지스터 간 데이터 이동과 연산을 중심으로 설계, 클럭 신호 포함. | 논리적 설계 및 합성(Synthesis) 대상 |

| 게이트 수준 | 게이트(NAND, NOR 등)의 연결로 회로를 기술. | 물리적 구현 전에 세부 설계 검증 |

| 물리적 수준 | 실제 반도체 배치를 다룸. 배선과 트랜지스터 크기까지 기술. | 실리콘 레벨 설계 및 제조 |

RTL 설계의 예제

(1) 간단한 레지스터 연산 예제

RTL 수준의 Verilog 코드로, 두 레지스터 값(A, B)을 더해 결과를 출력 레지스터(C)에 저장하는 동작을 정의합니다.

설명:

- 클럭 신호(posedge clk)가 들어오면 A와 B의 값을 더하고 C에 저장.

- 조합 논리(ADD 연산)와 레지스터(C)가 상호작용.

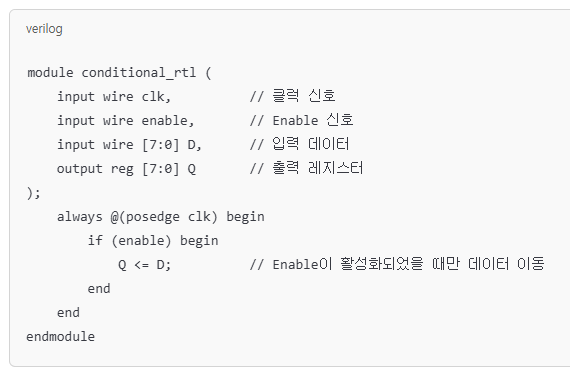

(2) 조건부 데이터 이동 예제

Enable 신호가 활성화될 때만 레지스터 값이 갱신되는 조건부 데이터 이동입니다.

설명:

- Enable 신호가 1일 때만 레지스터 Q가 입력 데이터 D로 갱신됩니다.

RTL의 역할

- 논리 합성(Synthesis)

- RTL 수준의 설계는 논리 합성 도구를 통해 게이트 수준의 설계로 변환됩니다.

- 이 과정에서 배선, 최적화, 전력 계산 등이 수행됩니다.

- 기능적 검증(Functional Verification)

- RTL 설계는 테스트 벤치를 사용해 시뮬레이션되고, 기능적 정확성을 확인합니다.

- 하드웨어 이해

- RTL은 추상적인 알고리즘을 하드웨어 동작으로 변환하는 중요한 단계로, 하드웨어와 소프트웨어 설계자 간의 협업을 용이하게 합니다.

결론

RTL(Register-Transfer Level)은 디지털 설계에서 레지스터 간 데이터 이동과 클럭 기반 동작을 기술하는 중요한 설계 단계입니다. 이는 설계자가 추상적인 동작을 논리 회로로 변환하기 위한 핵심적인 방식이며, Verilog/VHDL을 사용해 기술하고 합성을 통해 실제 회로로 구현됩니다.